開關電源的高性能電壓型PWM比較器

隨著科學技術的迅猛發展,電器設備日新月異,趨向小型化、低功耗、高效率,使開關電源需求日益增大,對電源的要求越來越高。

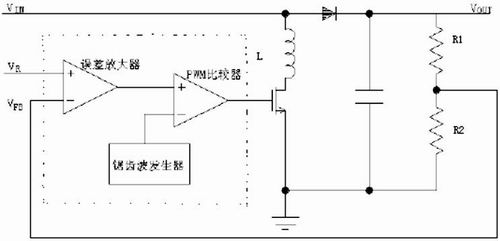

開關電源采用功率半導體器件作為開關,通過PWM控制開關的占空比來調整輸出電壓。根據定頻控制方式分為電壓型和電流型PWM控制,由于電壓型PWM控制方式具有結構簡單、易于實現等優點被廣泛應用。圖1所示是電壓控制型開關電源的原理圖,其中虛框部分是控制芯片內部結構。

圖1 電壓控制模式開關電源工作原理圖

從圖中可以看出,控制芯片有一個采用PWM調制法的電壓閉環反饋,將電壓誤差放大器放大后的直流信號與恒定頻率的三角斜波進行比較。根據脈寬度沖調制原理,得到需要的一定占空比脈沖寬度,推動開關功率管的開與關,經變壓器耦合后得到恒定的輸出電壓。控制芯片的核心電路是PWM比較器,脈沖寬度調制信號就是由PWM比較器產生。芯片的控制速度、效率、功耗很大程度上都是由PWM比較器決定。文中設計并實現了一種新型高性能的開關電源電壓型PWM比較器,具有較低輸入失調電壓、轉換速率快、較低功耗和波形更陡。

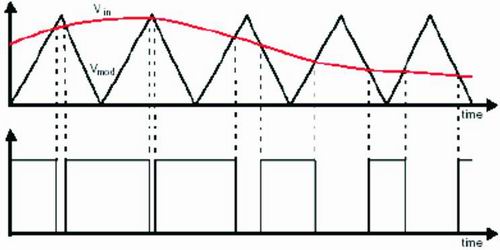

圖2是電壓型PWM比較器工作波形,輸入三角波接在比較器的反向輸入端,誤差放大器的輸出信號送至比較器同相輸入端,經放大后輸出PWM信號。

圖2 PWM工作波形圖

PWM比較器電路設計

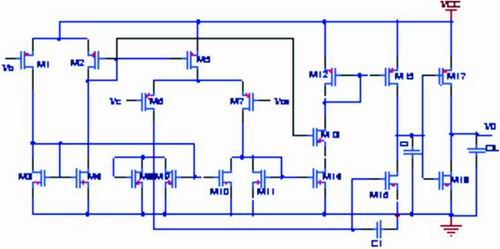

設計的PWM比較器電路原理圖如圖3所示。集成電路對比較器的性能要求是從響應速度、輸入失調電壓、功耗和面積幾個方面來考慮的。

圖3 PWM比較器電路圖

電路中VC為控制信號,是比較器的同相輸入端; VOS為振蕩器產生的鋸齒波信號,是比較器的反相輸入端;Vb作為電路中的偏置信號,提供差分對管的偏置和有源負載;最后經過反相器輸出脈沖寬度調制信號V0。圖3中三個電容是為計算延遲時間畫出的等效電容。

該電路用兩個尺寸完全一致的具有低驅動電流能力的PMOS管作為差分輸入管,它們分別控制兩個NMOS管M9和M10,當VC電壓值較低時,M10的柵電壓較高,M9則處于臨界導通狀態,所以V0輸出高電平。圖中M8是為了防止M9柵電壓過高時電流過大所設置的。該電路是雙端輸入轉單端輸出的放大電路,經差分放大后輸出的微弱信號,由于信號弱,輸出電壓擺幅小,加入了共源共柵放大電路,末級反相器是為了增加電路的負載能力。

系統輸入失調電壓

電路的輸入失調電壓是元器件參數值的不相同造成的,其中主要是兩個輸入管閾值電壓、導通電阻等區別產生的。為了減小工藝誤差對電路性能的影響,兩個輸入PMOS管的面積需要做得很大,來補償摻雜濃度、溝道調制效應、氧化層電荷密度等因素起伏的影響,本電路中采用輸入PMOS管的寬長比為300mm/6mm。

對系統輸入失調電壓的推導,假設電路完全平衡,即Vp的輸入能以和Vn輸入相同的方式傳送到輸出端。所以,M6、M7管完全匹配,M9、M10流過M5的電流被平分流過M6、M7。即:

根據M9和M5尺寸比,可得M9的電流。同理,可得M10電流,i10電流按M16和M4尺寸比鏡像到i16。即:

由平衡條件可知, 即

考慮溝道調制效應可得系統增益:

由 ,可得系統輸入失調電壓

,可得系統輸入失調電壓 。

。

從上面公式可見,在工藝參數一定的情況下,增益和失調電壓成反比,這就要求從幾個方面綜合考慮。相比之下,90倍的增益就已經滿足需要了。為了減小輸入失調電壓,可以縮小M6的寬長比。

經仔細調整各個MOS管的寬長比,綜合仿真檢測,系統失調電壓僅為0.118mV。

比較器速度

電路的反應速度與輸入信號差的絕對值有關,該絕對值越大,反應速度也越快。該反應速度還與偏置電壓有關,Vb電平很高時,差分對管流過的電流越小,對后級MOS管柵電容充放電的速度越小,比較器的反應速度降低。當Vb電平很低時,M11的偏置電壓也較低,同樣比較器的反應速度要下降。

比較器速度是由給寄生電容和電路電容充放電電流大小確定的。圖3畫出了比較器的主要寄生電容。C1是由M2與M4的漏擴散區造成的總耗盡電容;C2是由耗盡電容C1和柵源電容Cgs組成。

比較器的傳輸延遲主要是由三級延遲構成,第一級延遲是VDO從靜態工作點跳變到第二級跳變點VTRP2所用時間。假設驅動第二級器件在跳變過程中大部分時間處于飽和區,近似認為有一恒定電流驅動寄生負載電容。求得第一級延遲為:

其中

第二級的延遲是在第一級延遲時間結束時輸出一個階躍變化的信號,從輸出任一電源跳變到下級跳變電壓的時間計算出來,因而確定第二級輸出速度。 求得第二級延遲為:

同樣,第三級的延遲是由輸出反相器產生的,延遲時間的計算主要是根據輸入電壓上升到50%與輸出電壓下降到50%的時間延遲。

因此,電路的總延遲為:

電路的功耗

電路的功耗不僅與偏置信號Vb的電平有關,還與兩個進行比較的信號電平值有關,具體為Vb電平越低,電路功耗越大;輸入的兩個信號電平越低,電路功耗也越大。

仿真結果分析

根據以上的分析和計算,本文采用1.2μm CMOS工藝的HSPICE模型參數,對該電壓型比較器性能進行了幾個參數的仿真,電源電壓為3V。在仿真開始時,所有器件都取其最小值,仿真過程中,根據需要和電路功能參數來調整。先確定i7之后,逐一調整M6和M7來滿足輸出電壓擺幅,使器件工作在飽和狀態。

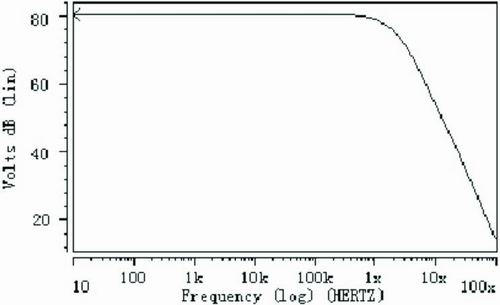

根據圖3,PWM比較器的正端輸入是1MHz的鋸齒波信號,要求在-3db時頻寬要大于1MHz。調整后經仿真得到PWM比較器小信號仿真波形,如圖4所示。增益達到了80db,在-3db頻寬接近1MHz,截至頻率大于100MHz。

圖4 PWM比較器小信號波形

在圖3中,加入差分對管可提升轉換的速率,加快比較器的翻轉。在輸出3V時,上升時間約4ns,下降時間約5.5ns,完全滿足在1MHz工作頻率的高性能要求。

圖5是調整后整體電路的輸出仿真波形圖,從仿真輸出波形圖中可以看出,PWM波形較陡峭,穩定性好,尖峰小,電路總功耗僅有618mW。

圖5 PWM比較器輸出波形和輸入波形

結語

通過對整個PWM比較器總體電路結構分析和計算,采用多路電流源代替傳統的電阻負載,輸入采用差動放大電路,結合開關電源的最新設計技術,設計出一種新型開關電源電壓型PWM比較器。該電路可以作為一個模塊電路直接運用在開關電源的電壓型控制芯片設計中,提高設計芯片的整體性能和系統集成化。設計的電路在1.2mm CMOS工藝下實現,仿真結果表明,電路各項指標達到了預期的要求。