三維集成電路的第一代商業應用,CMOS圖像傳感器和疊層存儲器,將在完整的基礎設施建立之前就開始。在第一部分,我們將回顧三維集成背后強大的推動因素以及支撐該技術的基礎設施的現狀,而在第二部分(下期),我們將探索一下三維集成電路技術的商業化。

不論是在需要考慮柵極和互連延遲的器件級別,還是在需要考慮帶寬和時序問題的系統級別,都無法避免一場正在發生的完美風暴,它要求業界在如何實現微電子功能方面做出轉變。影響這一轉變的關鍵因素包括國際半導體技術藍圖(ITRS)的推遲,以及由難于集成多孔低k材料所帶來的銅和低k線尺寸持續縮減的問題。與此同時,高達50%的功耗用在芯片的互連線上,即使對于65nm工藝節點的銅互連線來說,引線電阻和寄生電容也已經成為問題。

最早認識到這些問題是在2001年,當時IEEE院士Saraswat、Rief和Meindl預測,“芯片互連恐怕會使半導體工業的歷史發展減速或者止步……”,并提出應該探索電路的3D集成技術。

2007年9月,半導體工業協會(SIA)宣稱:“在未來大約10-15年內,縮小晶體管尺寸的能力將受到物理極限的限制”,因此3D集成的需求變得更加明顯。全新的器件結構,比如碳納米管、自旋電子或者分子開關等,在10-15年內還不能準備好。5新型組裝方法,如3D集成技術再次被提了出來。

存儲器速度滯后問題是3D集成的另一個推動因素,眾所周知,相對于處理器速度,存儲器存取速度的發展較慢,導致處理器在等待存儲器獲取數據的過程中被拖延。在多核處理器中,這一問題更加嚴重,可能需要將存儲器與處理器直接鍵合在一起。

3DIC集成技術的拯救

2005年2月,當《ICsGoingVertical》發表時,幾乎沒有讀者認識到發生在3DIC集成中的技術進步,他們認為該技術只是疊層和引線鍵合,是一種后端封裝技術。

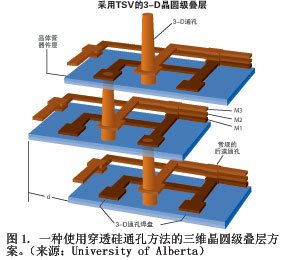

今天,3D集成被定義為一種系統級集成結構,在這一結構中,多層平面器件被堆疊起來,并經由穿透硅通孔(TSV)在Z方向連接起來(圖1)。

為制造這樣的疊層結構,已經開發了很多工藝,下面所列的正是其中的關鍵技術:

TSV制作:Z軸互連是穿透襯底(硅或者其他半導體材料)而且相互電隔離的連接,TSV的尺寸取決于在單層上需要的數據獲取帶寬;

層減薄技術:初步應用需減薄到大約75~50μm,而在將來需減薄到約25~1μm;

對準和鍵合技術:或者芯片與晶圓(D2W)之間,或者晶圓與晶圓(W2W)之間。

通過插入TSV、減薄和鍵合,3DIC集成可以省去很大一部分封裝和互連工藝。然而,目前還未完全明確,這些在整個制造工藝中需要集成在什么位置。似乎對于TSV工藝,可以在IC制造和減薄過程中,經由IDM或晶圓廠獲得,而鍵合可以由IDM實現,也可以在封裝操作中由外部的半導體組裝和測試提供商(OSATS)實現,但這有可能在技術成熟時發生變化。

在將來很有可能發生的是,3DIC集成技術會從IC制造與封裝之間的發展路線發生交疊時開始。

3D工藝選擇

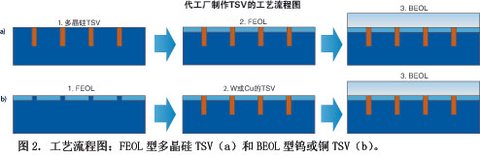

TSV可以在IC制造過程中制作(先制作通孔,viafirst),也可以在IC制造完成之后制作(后制作通孔,vialast)。在前一種情況下,前道互連(FEOL)型TSV是在IC布線工藝開始之前制作的,而后道互連(BEOL)型TSV則是在金屬布線工藝過程中在IC制造廠中實現的。

FEOL型通孔是在所有CMOS工藝開始之前在空白的硅晶圓上制造實現的(圖2)。使用的導電材料必須可以承受后續工藝的熱沖擊(通常高于1000℃),因而只能選用多晶硅材料。在BEOL過程中制造的TSV可以使用金屬鎢或銅,而且在通常情況下,制作流程處于整個集成電路工藝的早期,以保證TSV不會占據寶貴的互連布線資源。在FEOL和BEOL兩種情況下,TSV都必須設計進IC布線之中。

TSV也可以在CMOS器件制造完成之后制作。在鍵合工藝之前完成,或者在鍵合工藝之后完成。由于CMOS器件已經制作完成,因此在通孔形成時晶圓不需要再經受高溫處理,所以可以使用銅導電材料。很明顯,制作這些通孔的空白區域需要在設計芯片時就予以考慮。

如果可以選擇,無論是FEOL還是BEOL方案,只要是在晶圓代工廠制作TSV,都是相對簡單的選擇。BEOL互連層是一個擁有不同介質和金屬層的復雜混合體。刻蝕穿透這些層很困難,而且是由不同產品具體決定的。在完整的IC制造之后通過刻蝕穿透BEOL層來制作TSV會阻礙布線通道,增加布線復雜性并增加芯片尺寸,可能會需要一個額外的布線層。既然諸如TSMC(中國臺灣省臺北)和特許(新加坡)等晶圓廠已宣稱他們有意向量產化TSV制造,那么在IC制造工藝中制作通孔將成為一個更切實可行的選擇。

減薄

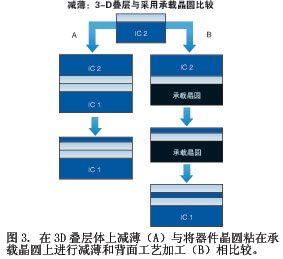

大多數3DIC工藝中,單個IC的厚度都遠低于75μm。減薄器件晶圓有兩種選擇(圖3)。在工藝A中,晶圓2以正面朝下的方式直接與IC疊層鍵合在一起。該晶圓接著被減薄到所需厚度,可能將TSV的背端露出。背面工藝順序刻蝕出通孔(如果沒在晶圓加工廠中實現的話),并制作出背面I/O焊盤。這樣的疊層減薄也可以使用已知良好芯片(KGD)而非整個晶圓,以正面朝下的方式與芯片疊層鍵合。

在工藝B中,晶圓首先粘在一個臨時承載晶圓上,通常是硅晶圓或者玻璃晶圓,之后進行減薄和背面工藝。IC晶圓以正面朝向承載晶圓的方式被粘合,因而必須在后面以正面朝上的方式與3DIC疊層鍵合在一起。由于晶圓與承載晶圓的臨時鍵合是通過有機膠完成的,后續的工藝步驟需要限制在該有機膠穩定的溫度范圍內。

在減薄和最終的背面工藝完成之后,器件晶圓可與疊層進行對準和鍵合,之后與承載晶圓分離(晶圓到晶圓鍵合),或者器件晶圓經由承載晶圓直接釋放到劃片框的劃片膠帶上,KGD可以進行后續操作。

對像存儲器這樣單片成品率高、芯片尺寸一致的晶圓來說,W2W是最合適的。D2W鍵合則是用于單片成品率低和/或芯片尺寸不同的晶圓。由于D2W鍵合之后就無法繼續利用整片晶圓進行低成本加工的特性,因此何時完成D2W組裝非常關鍵。

形成通孔

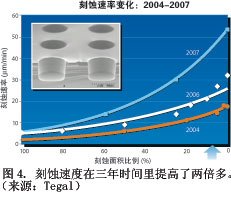

目前“鉆蝕”TSV的技術主要有兩種,一種是干法刻蝕或稱博世刻蝕,另一種是激光燒蝕(表1)。博世工藝十多年為MEMS工業而開發,快速地在去除硅的SF6等離子刻蝕和實現側壁鈍化的C4F8等離子沉積步驟之間循環切換。通過圖4可以看出,在過去幾年里,刻蝕速度穩步提高。

對于激光技術的重大進展,三星(韓國,首爾)已經在存儲器疊層中采用了這一技術。大多數最新數據都來自于Xsil(愛爾蘭,都柏林)的AlexeyRodin及其同事。作為一種不需掩膜的工藝,激光加工避免了光刻膠涂布、光刻曝光、顯影和去膠等工藝步驟。然而,未來當TSV尺寸降到10μm以下時,激光鉆孔是否可以進一步縮小,目前來看還存在一些問題。

通孔絕緣

通常氧化物(SiO2)絕緣層可以使用硅烷(SiH4)或TEOS通過CVD工藝沉積獲得。如果TSV在芯片制造之后進行絕緣和填充,則需要小心選擇沉積溫度。為獲得具有合適密度的功能性絕緣層,典型的TEOS沉積溫度在275-350℃范圍。

諸如CMOS圖像傳感器和存儲器等應用,則要求更低的沉積溫度。Alcatel(近期剛被Tegal收購,加州Petaluma)和其他的一些設備制造商最近開發了這類低溫氧化物沉積技術。IMEC(比利時魯汶)曾報道使用Parylene前驅體,可以在室溫下進行沉積,可作為TSV的高效有機絕緣層。

阻擋層、種子層和填鍍

阻擋層、種子層和電鍍技術的性能取決于通孔的尺寸和深寬比(AR)。不管是從制作盲孔方面考慮,還是從填孔方面考慮,清楚不同通孔尺寸下所需的深寬比要求非常重要。大多擁有成本(CoO)模型顯示,通孔制作和通孔填充是3D集成的主要成本障礙,但這明顯取決于通孔尺寸、節距和深寬比。盡管設備供應商和材料供應商正在努力研究10:1到20:1的深寬比,但在短期內,這樣的深寬比將在何種應用中使用尚不明確。

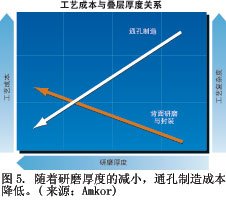

Amkor(亞利桑那州Chandler)的研究顯示,使用較薄的電路層,結合較小尺寸的通孔,可以實現較低的CoO,因為這些深寬比較低的通孔對應制造成本較低(圖5)。

隨著3D技術的演化以及應用中通孔尺寸和節距的縮小,疊層中每層的厚度也很有可能會減小。截至目前的測試表明,即使將硅片厚度減到5μm以下,電路性能也不會惡化。因此,很有可能的是,可制造性而非電學性能將成為未來的限制因素。此外,當考慮先通孔或后通孔方案時,厚度變得很重要。后者在硅刻蝕開始之前,需要先額外刻蝕厚度超過6μm的后道介質層。對于薄硅層來說,這將對刻蝕的深寬比造成很大影響。

諸如CMOS圖像傳感器、存儲器、邏輯電路上存儲器之類3D應用,在未來2-3代內都不會需要使用大于5的深寬比。在TSV尺寸降到約1μm甚至更小之前,我們將不會看到深寬比達到10-20范圍。

銅通孔中,TiN粘附/阻擋層和銅種子層都通過濺射來沉積。然而,要實現高深寬比(AR>4:1)的臺階覆蓋,傳統的PVD直流磁控技術效果并不令人滿意。基于離子化金屬等離子體(IMP)的PVD技術可實現側壁和通孔底部銅種子層的均勻沉積。由于沉積原子的方向性以及從通孔底部到側壁濺射材料過程中離子轟擊的使用,IMP提供更好的臺階覆蓋性和阻擋層/種子層均勻性。

晶圓鍵合技術選擇

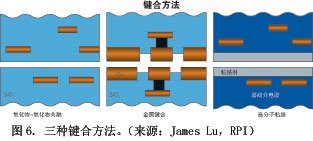

針對3D集成而考察的晶圓鍵合技術包括:

氧化物(SiO2)共熔鍵合

金屬-金屬鍵合

銅-銅共熔鍵合

共晶鍵合(Cu/Sn)

凸點技術(Pb/Sn、Au、In)

高分子粘結鍵合

由于特征尺寸的限制,圖6所示全部鍵合技術都需要特別光滑、平整和潔凈的表面。盡管所有這些技術看起來都可行,但有一種趨勢是轉向使用金屬-金屬鍵合技術,因為這種技術可以同時實現機械和電學的接觸界面。銅-銅鍵合直接銅鍵合工藝需要到在350-400℃溫度下施加壓力超過30分鐘,接著在350-400℃下的氮氣氣氛退火30-60分鐘。這一工藝需要高度拋光的銅表面并保持很高的潔凈度。像EVGroup(奧地利St.Florian/Inn)和SUSSMicroTec(佛蒙特州,Waterbury)等廠商提供的商業化工具,需要在單個對準工具上裝有多個鍵合頭,才能得到可接受的產能。一種像Ziptronix(北卡羅來納州,Morrisville)報道的稱作直接鍵合互連(DBI)的工藝,據說可以大大提高這一產能。這種技術使用金屬對TSV進行封帽,之后采用氧化物、金屬同步CMP進行平坦化,經過專利保護的表面處理技術,可使用標準的鍵合/對準機在大氣環境下1-2分鐘內實現芯片或者晶圓的鍵合。在350℃溫度下施加壓力,在低CoO鍵合操作下可以獲得了單一的金屬界面。

3D應用

表2總結了九種不同的3D集成工藝流程,都對應從晶圓工藝一直到鍵合。

本文的第二部分將重點對3D技術商業化過程中的重點參與者進行介紹。將會介紹3D集成的可能應用領域,比如存儲器與邏輯電路、閃存疊層以及其他的一些重點方向。

參考文獻:

1. A. Braun, “Low-k Bursts Into the Mainstream…Incrementally,” Semiconductor International, May 2005, p. 41.

2. K. Saraswat, “3D IC's: Motivation, PeRFormance Analysis and Technology,” 3D Architectures for Semiconductor Integration & Packaging, Phoenix, June 2005.

3. S. Vitkavage and K. Monnig, “3D Interconnects and the IRTS Roadmap”, Proc. 3D Architecture for Semiconductor Integration and Packaging Conf., Phoenix, 2005.

4. J.A. Davis et al., “Interconenct Limits on Gigascale Integration in the 21st Century”, Proc. IEEE, Vol. 89, 2001, p. 305.

5. P. Garrou, “3D Integration Invades Whitefish Montana,” Perspectives From the Leading Edge, Sept. 7, 2007.

6. P. Morrow et al., “Design and Fabrication of 3D Microprocessors,” MRS Proc., Vol. 970, Enabling Technologies for 3D Integration, C.Bower, P. Garrou, P. Ramm, K. Takahashi Eds., 2007, p. 91.

7. P. Garrou, “Future ICs Go Vertical,” Semiconductor International, February 2005, p. SP10.

8. P. Garrou, “3D IC Integration: Evolution or Revolution?”, Perspectives From the Leading Edge, March 16, 2008.

9. P. Garrou, “ASET Drives 3D Integration Workshop in Tokyo,” Perspectives From the Leading Edge, June 21, 2008.

10. P. Garrou, “Going Vertical in Whitefish,” Sept. 9, 2007; “High Throughput Laser Drilling for 3D IC TSV,” Feb. 17, 2008, Perspectives From the Leading Edge.

11. P. Garrou, “3D Equipment & Materials Vendors Consortium,” Perspectives From the Leading Edge, Aug. 26, 2007.

12. P. Garrou, “3D Practitioners Assemble at Fort McDowell,” Perspectives From the Leading Edge, March 23, 2008.

13. P. Garrou, “NXP Proposes Passive Integration in 3D IC Stacks,” Perspectives From the Leading Edge, April 13, 2008.

14. P. Garrou, “More 3D Integration at ECTC 2008,” Perspectives From the Leading Edge, June 28, 2008.

15. P. Garrou, “If It's Thursday It Must Be San Jose,” Perspectives From the Leading Edge, June 8, 2008.

16. D.M. Jang et al., 57th Electronic Component Tech. Conf. 2007, p. 847.

17. P. Garrou, “3D Road Tour Continued,” Perspectives From the Leading Edge, May 28, 2008.

18. Handbook of 3D Integration, P. Garrou, P. Ramm & C. Bower Eds., Wiley-VCH.

來源:EDN

http:www.mangadaku.com/news/2009-5/20095995851.html