——王浪 應用工程師

Silicon Labs ((芯科實驗室有限公司,簡稱Silicon Labs)) TIMING 產品推出市場以來,因其優異的去抖性能、靈活的任意頻點的配置、比競爭對手縮短一半的交貨周期而獲得廣泛的應用。Silicon Labs 專利DSPLL技術作為每一款Silicon Labs TIMING 產品的核心,使Silicon Labs產品具有了超越競爭對手的優異性能。下面將詳細介紹DSPLL 的原理和特點。

1. DSPLL 的原理

這項技術運用DPS 高速運算替代通常采用的分離器件搭建的鎖相環濾波電路。由于不需要外接器件,單板的噪聲對鎖相環影響降低到最低。這項數字技術能夠在溫度,電壓變化和外圍MCU不同的情況下提供高度的穩定性和一致性。下圖是DSPLL 一個簡單功能框圖。

DSP運算處理 Phase Detector 的相差脈沖,產生一個數字頻率控制字M 來調制一個數字控制的時鐘DCO。數字分頻器N1,N2,N3 都有很大的范圍,這樣可以是在一個輸入頻率下,產生近似任意頻率的輸出。具有DSPLL技術的窄環路帶寬產品(Si5316, Si5319, Si5323, Si5326, Si5366, and Si5368) 提供超低的輸出抖動和極強的抖動衰減性能。對于那些需要多路低抖動時鐘頻率轉換的應用,寬環路帶寬的產品(Si5322, Si5325, Si5365, and Si5367) 是一種很好的選擇。

2. DSPLL帶來的優勢

(1)極低的輸出抖動 0.3ps RMS 抖動。

(2)寬范圍的輸入頻率和輸出頻率。

輸入頻率:2KHz-710MHz

輸出頻率:2KHz-1.4GHz

由于數字分頻器都有很大的范圍,才能保證寬范圍的輸入和輸出頻率。在搭建復雜的時鐘系統的時候,特別是作為一個時鐘平臺,應用在各種場合,只需要改變軟件和pin的管腳配置就可以完成,而競爭對手的芯片,就需要改變芯片的型號,重新進行設計。

(3) 可調的環路帶寬。 60Hz-8.4KHz,采用DSP 技術來做PLL的低通濾波器,帶來一個非常大的好處就是可以通過改變寄存器來調節環路帶寬,適用于多種信號質量的環境。

(4) 極低的相噪指標。 采用芯片內部集成濾波器,可以有效的降低來自單板的噪聲干擾。

(5) 集成度高,簡化了鎖相環的設計和布板

傳統的鎖相環芯片,需要客戶自己來設計低通的濾波器,還要做好低通濾波器的EMC 的防護措施,布板的時候也需要特別的注意。由于Silicon Labs PLL外圍基本上沒有什么器件,僅有一個作為reference 的時鐘輸入。芯片的設計有DSPLLsim軟件完成配置,布板沒有強制性要求。

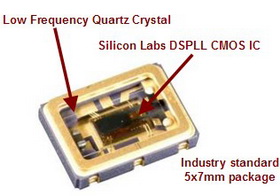

3. 基于DSPLL技術的XO和VCXO介紹

(1)Silicon Labs XO和VCXO 的特點

VCXO 和XO產品有任意定制頻率的單路,雙路,四路輸出系列。輸出頻率范圍10MHz-1.4GHz,可以任意定制。

——極低的輸出抖動和PSRR:

- 1

- 2

- 總2頁

來源:世強電訊

http:www.mangadaku.com/news/2010-6/2010630134134.html